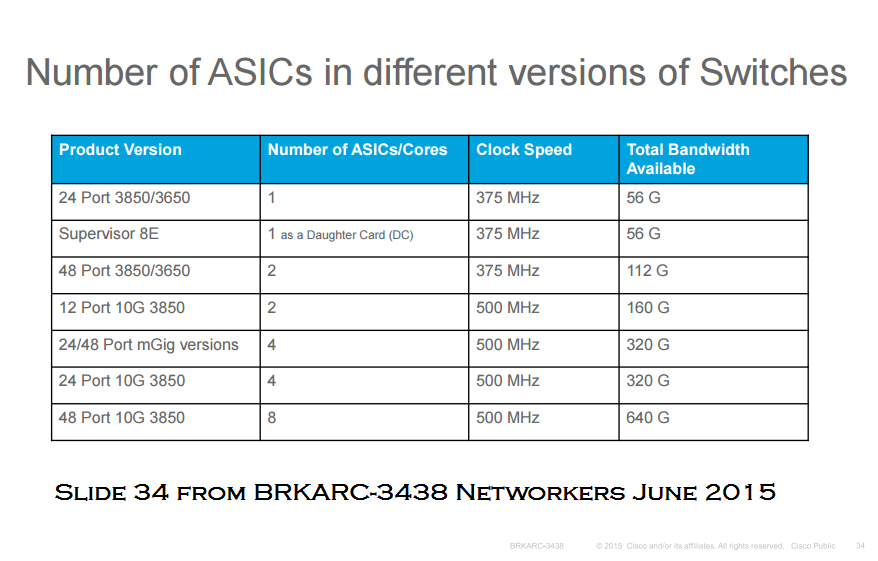

It is powered by the new UADP ASIC. UADP stands for Unified Access Data Plane. What is unified is that in addition to a shared memory switch function, the silicon runs the CAPWAP protocol in hardware to give really fast WiFi performance. Three of the UADP ASICs are used in the 5760 Wireless Lan Controller to provide 60 Gb/s of WiFi capacity. In the 3850 switches, an ASIC is used to host 24 ports. A 48 port switch has two UADP ASICs. The same ASIC runs the 3650, a version without the stacking capability.

It is remarkably difficult to get hard info on buffer allocations for this switch, although it appears to be available to those with a big checkbook:

| End-to-End QoS Network Design: Quality of Service for Rich-Media & Cloud Networks, 2nd Edition |

| By Tim Szigeti, Christina Hattingh, Robert Barton, Kenneth Briley Published Nov 26, 2013 by Cisco Press. Part of the Networking Technology series. |

In unrestricted public information Cisco has the following table that shows, from 20,000 ft, the progression of ASICs.

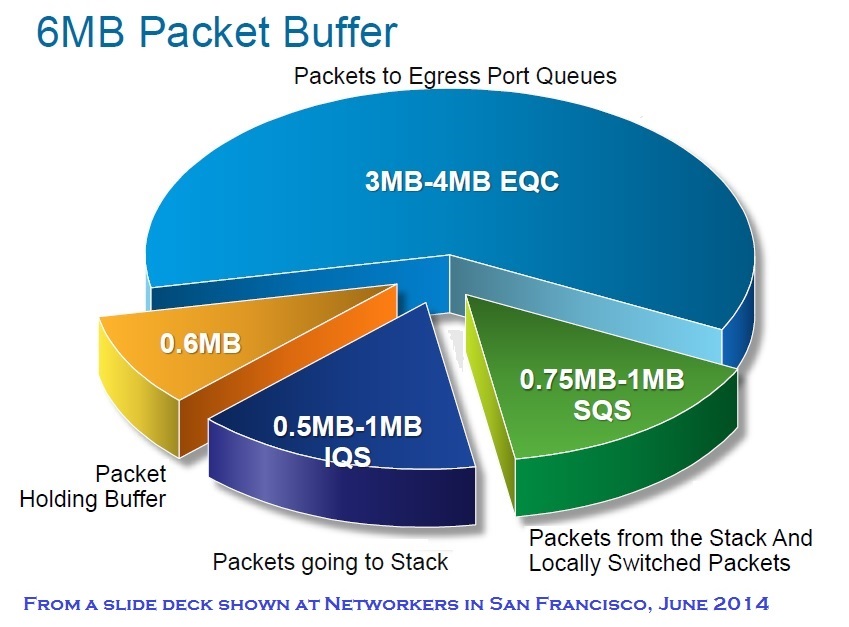

Above, Buffers/48 port means buffers in the 48 port switch. Twenty-four port models have half the packet buffers. A per-ASIC view of the 3850 ASIC buffer resources shows this: