#

# BCM56980 12.8 Tb/s Multilayer Switch

### Overview

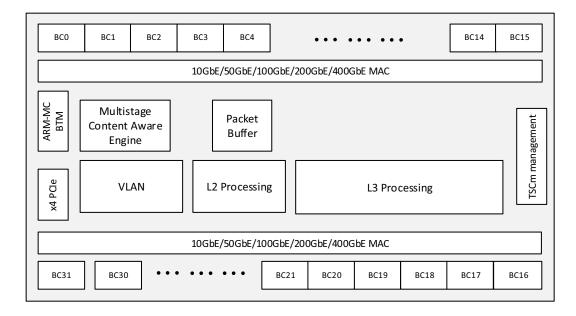

The Broadcom<sup>®</sup> BCM56980 family is a class of high-performance, high-connectivity network switching devices supporting up to 32x 400GbE, 64x 200GbE, or 128x 100GbE switch ports. The device family features a maximum of 32 integrated BlackhawkCores, each with eight integrated 50G PAM4 SerDes transceivers and associated PCS for native support of XFI, 10GBASE-KR/CR/SR/ER/LR, 40GBASE-KR4/CR4/SR4/ER4/LR4, 50GbE, and 100GBASE-KR4/CR4/SR4/ER4/LR4. The BCM56980 delivers high-bandwidth, glueless network connectivity up to 12.8 Tb/s on a single chip.

The BCM56980 is a family of Ethernet switches designed to address performance, capacity, and service requirements for next-generation data center and cloud computing environments. The BCM56980 architecture delivers complete Layer 2 (L2) and Layer 3 (L3) switching and routing capabilities with maximum port density, while consuming minimum power, latency, and board footprint. Software compatibility is maintained across the StrataXGS<sup>®</sup> product portfolio to simplify customer designs and reduce customer time-to-market.

As server interfaces transition to higher Ethernet speeds and virtualization continues to increase link utilization, data center networks are demanding switches with dense 100GbE and 400GbE connectivity at the edge and aggregation layers. With up to 256 50G PAM4 SerDes that conform to IEEE 802.3bs and 802.3cd specifications, and full flexibility in configuring 10/25/40/50/100/200/400GbE ports, a single BCM56980 switching chip can be used to build scalable, cost-effective Top of Rack (ToR) switch, blade switch, and aggregation equipment across the entire data center. The BCM56980 has extensive features to address the rapidly increasing scale of data center network deployments and distributed computing applications: large L2 and L3 forwarding capacity supporting numerous multipathing technologies; enhanced instrumentation; switching, migration, and robust buffer performance including manyto-one burst absorption capabilities that assist in TCP incast scenarios.

With the BCM56980 device, customers can build data centers with much higher server node counts while simultaneously improving per-port power efficiency. The BCM56980 is built using state-of-the-art silicon process technology and incorporates advanced power management features to minimize power based on the features in use.

### **Features**

General features:

- 256x 50G PAM4 SerDes configuration.

- Flexible port configurations: 10GbE to 400GbE support with run-time reconfigurability (Flexport<sup>™</sup>).

- Oversubscription to maximize I/O throughput.

- Low pin-to-pin latency in cut-through and store-and-forward modes.

- Supports IEEE 802.3bj Clause 91 Forward Error Correction (FEC), IEEE 802.3bj Clause 93 100GbE-KR4 transmit training, and IEEE 802.3ap Clause 72 10G-KR transmit training.

Data center features:

- Hardware-based encapsulation.

- DCBX congestion management: priority-based flow control (PFC), enhanced transmission selection (ETS).

- Per virtual machine traffic shaping.

StrataXGS scalable architecture supports high-performance switch designs for L2/L3 packet processing:

- Full IPv4 and IPv6 routing support.

- Hardware-based encapsulations, including MPLS, GRE, and ISATAP.

- Three-stage ContentAware<sup>™</sup> processing with ICAP stage supports exact match feature.

- Dedicated hash table for L2 MAC and L3 host.

- Flexible ingress/egress counter pools.

### Features (continued)

Buffering and traffic management:

- Integrated high-performance SmartBuffer memory for maximum burst absorption and service guarantees.

- Full Quality of Service (QoS) support:

- Weighted random early discard (WRED).

- srTCM and trTCM color marking and metering.

- Congestion management capabilities including ECN.

- Dynamic load balancing (DLB) for ECMP groups.

- Packetized MMU statistics.

- Network monitoring.

- Elephant trap monitors.

- DLB monitors.

- Latency distribution histogram.

- Network congestion detection.

- sFlow redirect.

- Visibility and packet tracing.

- Enhanced load balancing.

- Enhanced trunk hashing capabilities: RTAG7, symmetric hash, flex hash, and resilient hash.

- Support for jumbo frames up to 9416 bytes.

- High-speed vector-based scheduler with 12 queues per port and scheduling algorithms: SP, RR, WRR, and WDRR.

Additional features:

- In-band telemetry.

- Elephant trap.

- Comprehensive time synchronization support:

- Integrated IEEE 1588v2 processor.

- IEEE 802.1AS support.

- Synchronous Ethernet.

- Ingress and egress per packet time stamping.

- sFlow support includes ingress, egress, and flex sampler. Option to forward truncated sFlow packets to remote agent.

- Packet sampling (PSAMP) ingress-based mirroring with option to truncate as well as zero out the payload at different offset.

- Two dedicated 1G/10G auxiliary Ethernet ports

- x4 PCI Express (PCIe) Gen 3.0 interface to support a local CPU.

- Adjustable voltage scaling (AVS) for reduced average and peak power.

### Applications

- Data center ToR, blade, and aggregation switching.

- Mobile core switches.

- Cloud computing.

- Large-scale enterprise campus backbone.

- Service provider core switching.

#### Figure 1: 12.8 Tb/s Multilayer Switch

# **Table of Contents**

| Chap | oter 1: Introduction                                                     | 6  |

|------|--------------------------------------------------------------------------|----|

| Chap | oter 2: Device Overview                                                  | 7  |

| 2.1  | Feature List                                                             | 7  |

| 2.2  | Target Applications                                                      |    |

|      | 2.2.1 100GbE/200GbE/400GbE Aggregation Switch                            | 14 |

| Chap | oter 3: System Interfaces                                                | 15 |

| 3.1  | BlackhawkCore SerDes                                                     |    |

| 3.2  | BlackhawkCore Octal SerDes Configuration Guidelines                      |    |

|      | 3.2.1 Flexport Configuration                                             | 20 |

| 3.3  | 10G Quad MerlinCore SerDes                                               |    |

| 3.4  | PCIe                                                                     | 21 |

| 3.5  | LED                                                                      | 21 |

| 3.6  | MIIM                                                                     | 22 |

| 3.7  | Broadcom Serial Controller                                               |    |

| 3.8  | JTAG                                                                     | 23 |

| 3.9  | BroadSync                                                                | 23 |

|      | 3.9.1 Slave Mode – BroadSync Signals as Inputs                           | 24 |

|      | 3.9.2 Master Mode – BroadSync Signals as Outputs                         | 24 |

| Chap | oter 4: Signal Descriptions                                              | 25 |

| 4.1  | Pin Description                                                          | 26 |

| 4.2  | BCM56980 Pin List by Ball Number                                         |    |

| 4.3  | Device Differences                                                       |    |

| Chap | oter 5: Electrical Specifications                                        | 43 |

| 5.1  | Operating Conditions                                                     | 43 |

| 5.2  | Absolute Maximum Ratings                                                 |    |

| 5.3  | Power-Up and Power-Down Specifications                                   |    |

| 5.4  | Device Power Supply Requirement                                          |    |

| 5.5  | DC Characteristics                                                       |    |

|      | 5.5.1 Standard 3.3V Signals                                              | 46 |

|      | 5.5.2 Management Interface                                               | 46 |

|      | 5.5.3 BSC Interface                                                      | 46 |

|      | 5.5.4 Reference Clocks                                                   | 47 |

|      | 5.5.4.1 Core PLL Reference Clock (CORE_PLL_FREF)                         | 48 |

|      | 5.5.4.2 TimeSync PLL Reference Clock (TS_PLL_FREF)                       | 49 |

|      | 5.5.4.3 BroadSync PLL Reference Clocks (BS_PLL0_REFCLK / BS_PLL1_REFCLK) |    |

|      | 5.5.4.4 PCI Express PLL Reference Clock (PCIe_REFCLK)                    |    |

|      | 5.5.4.5 BlackhawkCore PLL Reference Clocks (BC*_REFCLK)                  |    |

| 5.5.4.6 MerlinCore PLL Reference Clock (MGMT_REFCLK)                 | 53 |

|----------------------------------------------------------------------|----|

| 5.5.5 PCIe                                                           |    |

| 5.6 AC Characteristics                                               | 55 |

| 5.6.1 Reset Timing                                                   |    |

| 5.6.2 Reference Clocks                                               |    |

| 5.6.2.1 Core PLL Reference Clock (CORE_PLL_FREF)                     |    |

| 5.6.2.2 TimeSync PLL Reference Clock (TS_PLL_FREF)                   |    |

| 5.6.2.3 BroadSync PLL Reference Clocks (BS_PLL0_FREF / BS_PLL1_FREF) | 57 |

| 5.6.2.4 PCI Express PLL Reference Clock (PCIe_REFCLK)                | 57 |

| 5.6.2.5 BlackhawkCore PLL Reference Clocks (BC*_REFCLK)              |    |

| 5.6.2.6 MerlinCore PLL Reference Clocks (MGMT_REFCLK)                |    |

| 5.6.3 BlackhawkCore (50G) Interface                                  |    |

| 5.6.4 MerlinCore (TSC4-M) Interface                                  |    |

| 5.6.4.1 MerlinCore Receiver                                          |    |

| 5.6.4.2 MerlinCore Transmitter                                       | 60 |

| 5.6.5 PCIe Interface                                                 | 61 |

| 5.6.5.1 PCIe Receiver Input                                          | 61 |

| 5.6.5.2 PCIe Transmitter Output                                      | 61 |

| 5.6.6 BroadSync Interface                                            | 62 |

| 5.6.7 BSC Interface                                                  | 63 |

| 5.6.8 LED Interface                                                  | 65 |

| 5.6.9 Management Interface (MIIM)                                    | 66 |

| 5.6.10 Synchronous Ethernet Interface                                | 67 |

| 5.6.10.1 L1_RCVRD_CLK and L1_RCVRD_CLK_BKUP Output Timing            | 67 |

| 5.6.11 JTAG Interface                                                |    |

| 5.6.12 QSPI Interface                                                |    |

| 5.6.13 SPI Interface                                                 |    |

| Chapter 6: Standard Electrical Characteristics                       | 72 |

| 6.1 PAM4 Electrical Characteristics                                  | 72 |

| 6.2 40G XLAUI Electrical Characteristics                             | 72 |

| 6.2.1 Transmitter                                                    | 72 |

| 6.2.2 Receiver                                                       |    |

| 6.3 10GBASE-KR Electrical Characteristics                            | 75 |

| 6.3.1 Transmitter                                                    | 75 |

| 6.3.2 Receiver                                                       | 75 |

| Chapter 7: Thermal Specifications                                    |    |

| 7.1 Thermal Requirements                                             | 76 |

| 7.2 Package Thermal Specifications                                   | 77 |

| 7.3 Heat Sink                                                        |    |

| 7.3.1 Heat Sink Selection         |    |

|-----------------------------------|----|

| 7.3.2 Heat Sink Attachment        |    |

| 7.4 On-Die Thermal Monitors       |    |

| Chapter 8: Mechanical Information |    |

| 8.1 4344-Ball FCBGA               | 80 |

| Chapter 9: Ordering Information   |    |

| 9.1 PB-Free Packaging             | 81 |

| Glossary                          |    |

| Related Documents                 |    |

| Revision History                  |    |

| 56980-DS111; July 19, 2019        |    |

| 56980-DS110; March 27, 2019       |    |

| 56980-DS109; January 17, 2019     |    |

| 56980-DS108; October 16, 2018     |    |

| 56980-DS107; July 5, 2018         |    |

| 56980-DS106; June 11, 2018        |    |

| 56980-DS105; May 17, 2018         | 89 |

| 56980-DS104; March 23, 2018       | 89 |

| 56980-DS103; January 4, 2018      | 89 |

| 56980-DS102; November 6, 2017     |    |

| 56980-DS101; August 31, 2017      |    |

| 56980-DS100; July 13, 2017        |    |

|                                   |    |

# **Chapter 1: Introduction**

The Broadcom BCM56980 family consists of several devices with flexible port configurations. All switching features and table sizes are identical within each device, except as noted in the following tables.

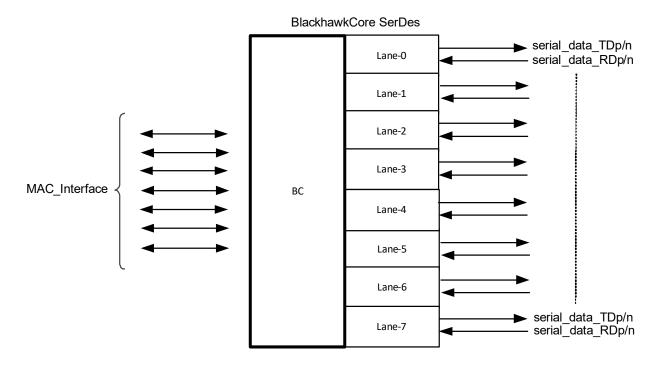

NOTE: The BCM56980 supports PAM4-based SerDes controller cores, BlackhawkCore (BC), and MerlinCore (TSCm).

| Device   | I/O Bandwidth<br>(Tb/s) | BC (#) | Dedicated Mgmt.<br>TSCm (#) | Typical Configuration           |

|----------|-------------------------|--------|-----------------------------|---------------------------------|

| BCM56980 | 12.8                    | 32     | 2                           | 32 × 400G, 128 × 100G           |

| BCM56982 | 8.0                     | 20     | 2                           | 20 × 400G, 48 × 100G + 8 × 400G |

| BCM56983 | 6.4                     | 16     | 1                           | 16 × 400G                       |

| BCM56984 | 6.4                     | 32     | 2                           | 64 × 100G (NRZ only)            |

Table 1: BCM56980 Family I/O Bandwidth and Throughput

The BCM56980 family includes the configurations described in the following table.

Table 2: BCM56980 Device Family Port Configurations

| Device   | 400 Gb/s   | 200 Gb/s   | 100 Gb/s    | 50 Gb/s     | 10 Gb/s     |

|----------|------------|------------|-------------|-------------|-------------|

| BCM56980 | 32 maximum | 64 maximum | 128 maximum | 144 maximum | 144 maximum |

| BCM56982 | 20 maximum | 40 maximum | 80 maximum  | 144 maximum | 144 maximum |

| BCM56983 | 16 maximum | 32 maximum | 64 maximum  | 72 maximum  | 72 maximum  |

| BCM56984 |            | -          | 64 maximum  | 128 maximum | 144 maximum |

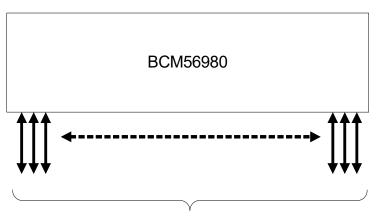

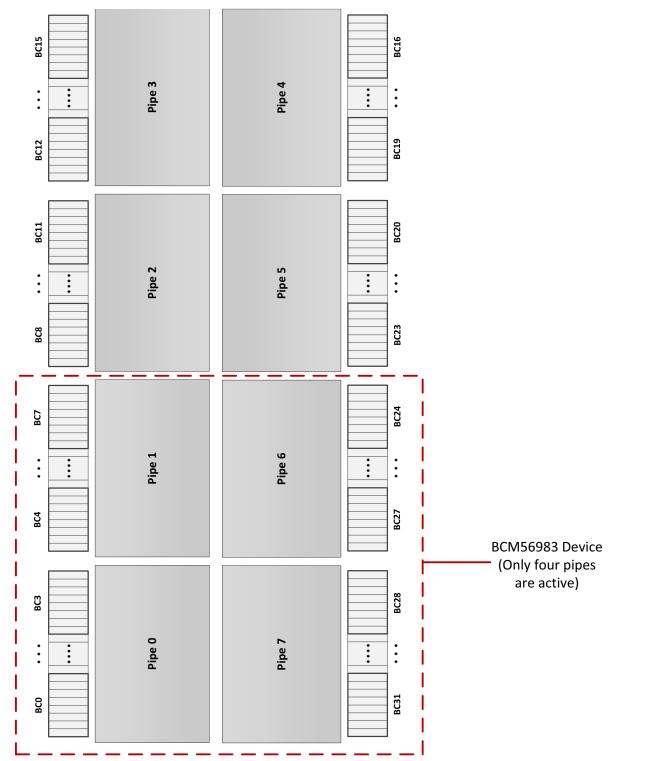

The BCM56980 supports a maximum of 144 front-panel ports by using 32 BlackhawkCores in the eight pipelines. Ports can be configured only as Ethernet ports.

**NOTE:** The BCM56983 uses only four of the eight pipelines, which reduces the supported number of front-panel ports to 72.

In addition to the BlackhawkCores, the device contains one MerlinCore that can be used to support a maximum of two auxiliary ports. The MerlinCore consists of four SerDes lanes. If an auxiliary port is configured in single SerDes lane mode, lane 0 or lane 2 should be used. If the port is configured as RXAUI mode, either lanes 0 and 1, or lanes 2 and 3 should be used. If a single auxiliary port is used, the four-lane XAUI port mode should be used.

The device also supports a four-lane PCIe interface that can be operated at Gen1, Gen2, and Gen3 speed. The PCIe interface is typically connected to the root complex of the host CPU as an x1, x2, or x4 PCIe Gen1, Gen2, or Gen3 interface.

# **Chapter 2: Device Overview**

The BCM56980 has a modular, high-performance packet-switching architecture and provides the following benefits:

- Flexible port configurations

- Scalable throughput

- Scalable packet processing features

- Low pin-to-pin latency

### 2.1 Feature List

The BCM56980 features are listed in the following table.

#### Table 3: BCM56980 Features

| Feature                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration             | <ul> <li>10/25/40/50/100/200/400GbE multilayer Ethernet switch.</li> <li>All ports operate in oversubscription mode.</li> <li>Flexible SerDes contains eight SerDes lanes per BlackhawkCore, configured to operate in any of the following configurations: <ul> <li>25GbE (1-lane)</li> <li>40GbE (2-lane)</li> <li>40GbE (4-lane)</li> <li>50GbE (1-lane)</li> <li>100GbE (2-lane)</li> <li>100GbE (2-lane)</li> <li>200GbE (4-lane)</li> <li>200GbE (4-lane)</li> <li>400GbE (8-lane)</li> </ul> </li> </ul> |

| L2 Switching              | <ul> <li>L2 learn cache for software based learning.</li> <li>Software-based MAC address aging.</li> <li>Supports Ethernet/IEEE 802.3 packet sizes (64 bytes to 1522 bytes) and jumbo packets up to 9416 bytes.</li> <li>Reserved MAC address table for CPU control packets, bridge protocol data units (BPDUs), and the ability to perform shared VLAN switching.</li> </ul>                                                                                                                                  |

| Switching                 | <ul> <li>Supports Ethernet/IEEE 802.3 packet sizes (64 bytes to 1522 bytes) and jumbo packets up to<br/>9416 bytes.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                 |

| L2 Multicast              | <ul> <li>Three port filtering modes (PFM) to control multicast packet behavior.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VLAN                      | <ul> <li>Supports 4K VLANs.</li> <li>Supports up to 128 VLAN profiles on a per VLAN basis.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          |

| VLAN                      | <ul> <li>Assign VLAN for untagged and priority tagged packets based on the following:         <ul> <li>Port-based VLANs.</li> </ul> </li> <li>Supports up to 128 VLAN profiles on a per VLAN basis.</li> <li>Ingress filtering for IEEE 802.1Q VLAN security.</li> </ul>                                                                                                                                                                                                                                       |

| Spanning Tree Group Table | Indicates spanning tree state of each port for each spanning tree group.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

### Table 3: BCM56980 Features (Continued)

| Total of four mirror-to-port (MTP) ports are supported. They are shared by ingress and egress mirroring logic. The device can support any combination of four mirroring port types.     A separate packet is created for each MTP port.     Mirror-to-port receives unmodified packet for egress mirroring.     Mirror-to-port receives unmodified packet for egress mirroring.     Encapsulate dremote switched port analyzer (RSPAN) mirroring, thus a GRE tunnel.     Multiple packets can be generated in the StrataXGS architecture: one packet for the switched copy, and four mirror copies which can be of any type.     Payload zeroing and truncation for mirrored copies.     DSCP emarking based on a FP filter match.     DSCP to IEEE 802.1 p mapping.     Remap incoming DSCP to new outgoing DSCP.     Layer 3 Routing     (IPv4, IPv6)     Native support for IPv4 and IPv6 unicast and multicast routing.     Direct-attached hosts in the L3 table.     Longest prefix match (LPM) based routing.     ECM/PWCMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow label, and TCP/UDP port.     Software-based aging support.     Software-based aging support of LPM.     Software-based aging support DPM aging and L3 routing.     Flexible multicast packet support of LPM multicast, and IPv6 multicast packets.     Control trapping of | Feature              | Description                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Iogic. The device can support any combination of four mirroring port types.         A separate packet is created for each MTP port.         Mirror-to-port receives modified packet for igness mirroring.         Mirror-to-port receives modified packet for igness mirroring.         Remote switched port analyzer (RSPAN) mirroring, VLAN mirroring into a GRE turnel.         Multiple packets can be generated in the StrataXGS architecture: one packet for the switched copy, and four mirror copies which can be of any type.         DSCP       Per port DSCP remarking.         DSCP intermarking based on a FP filter match.         DSCP intermarking.       DSCP to the mapping.         Remap incoming DSCP to new outgoing DSCP.         Layer 3 Routing       Native support for IPV4 and IPV6 uncleast and multicast routing.         [IPv4, IPv6)       Direct-attached hosts in the L3 table.         Longest prefix match (LPM) based routing.       ECMPAVCMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow label, and TCP/UDP port.         Software-based aging support.       Return 128-bit IPv6 support as well as /64 support for LPM.         Virtual Routing and       Segmentation of L3 routing tables.         Forwarding (VRF)       VPN ID assigned based on ingress port, VLAN, or flow.         IP Multicast       Simultaneous L2 bridging and L3 routing.         Flexible multicast address consistency check with destinution MAC address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Mirroring            |                                                                                                                                                                                                             |

| <ul> <li>Mirror-to-port receives unmodified packet for ingress mirroring.</li> <li>Mirror-to-port receives modified packet for egress mirroring.</li> <li>Remote switched port analyzer (RSPAN) mirroring VLAN mirroring (NLAN mirroring)</li> <li>Encapsulated remote switched port analyzer (RSPAN) mirroring into a GRE turnel.</li> <li>Multiple packets can be generated in the StrataXCS architecture: one packet for the switched copy, and four mirror copies which can be of any type.</li> <li>Payload zeroing and truncation for mirrored copies.</li> <li>DSCP</li> <li>Per port DSCP remarking based on a FP filter match.</li> <li>DSCP to IEEE 802.1 p mapping.</li> <li>Remap incoming DSCP to new outgoing DSCP.</li> <li>Layer 3 Routing</li> <li>Native support for IPv4 and IPv6 unicast and multicast routing.</li> <li>Direct-fatched hosts in the L3 table.</li> <li>Longest prefix match (LPM) based routing.</li> <li>E CMP/N/CMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow label, and TCP/UDP port.</li> <li>Software-based aging support.</li> <li>Rotuting of IPv6 packets.</li> <li>True 128-bit IPv6 support as well as /64 support for LPM.</li> <li>Virtual Routing and</li> <li>Segmentation of L3 routing tables.</li> <li>Forwarding (VRF)</li> <li>VPN ID assigned based on ingress port, VLAN, or flow.</li> <li>IP Multicast</li> <li>Simultaneous L2 bridging and L3 routing.</li> <li>Flexible multicast packet replication.</li> <li>Optional source port checks.</li> <li>Dual lookup; (S, G, V) and (*, G, V).</li> <li>Ability to fall back to L2 multicast lookup on IPMC miss.</li> <li>Port filter mode (PKM) per VLAN for L2 multicast, and IPv6 multicast packets.</li> <li>Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.</li> <li>IP multicast address consistency check wit destination MAC address.</li> <li>IP multicast address consistency check wit des</li></ul>                                                                                                                  |                      | <ul> <li>Total of four mirror-to-port (MTP) ports are supported. They are shared by ingress and egress mirroring<br/>logic. The device can support any combination of four mirroring port types.</li> </ul> |

| • Mirror-to-port receives modified packet for egress mirroring.           • Remote switched port analyzer (RSPAN) mirroring, flow mirroring           • Remote switched port analyzer (RSPAN) mirroring, flow mirroring           • Multiple packets can be generated in the StrataXGS architecture: one packet for the switched copy, and four mirror copies which can be of any type.           • Paryotal zeroing and truncation for mirrored copies.           DSCP         • Per port DSCP remarking.           • Remap incoming DSCP to mew outgoing DSCP.           Layer 3 Routing         • Native support for IPv4 and IPv6 unicast and multicast routing.           (IPv4, IPv6)         • Native support for IPv4 and IPv6 unicast and multicast routing.           • Direct-attached hosts in the L3 table.         • Longest prefix match (LPvH) based couting.           • ECMPMCMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow label, and TCP/UDP port.           • Software-based aging support.         • Routing of IPv6 packets.           • True 122b-II Pv6 Simport as well as /64 support for LPM.           Virtual Routing and Forwarding (VRF)         • VPN ID assigned based on ingress port, VLAN, or flow.           • VPN ID assigned based or is IPv6, and the payload is IPv6 multicast packets.           • Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.           • IP Multicast         • IPv6-In-IPv6: The outer header is IPv6, and the payload is IPv6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      | <ul> <li>A separate packet is created for each MTP port.</li> </ul>                                                                                                                                         |

| Permote switched port analyzer (RSPAN) mirroring, VLAN introring, into a GRE tunnel.           Encapsulated remote switched port analyzer (RSPAN) mirroring into a GRE tunnel.           Multiple packets can be generated in the StrataXGS architecture: one packet for the switched copy, and four mirror copies which can be of any type.           DSCP         Per port DSCP remarking.           DSCP to IEEE 802.1 pmapping.         Remap incoming DSCP to new outgoing DSCP.           Layer 3 Routing         Native support for IPv4 and IPv6 unicast and multicast routing.           (IPv4, IPv6)         Direct-attached hosts in the 13 table.           Longest prefix match (LPM) based routing.         ECMPWCMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow label, and TCP/UDP port.           Software-based aging support.         Routing (IPv6)           Virtual Routing and         Segmentation of L3 routing tables.           Forwarding (VRF)         VPN ID assigned based on ingress port, VLAN, or flow.           IP Multicast         Simultaneous L2 bridging and L3 routing.           Pieklble multicast packet replication.         Optional source port checks.           Dual lookup: (S, G, V) and (*, G, V).         Ability to fall back to L2 multicast lookup on IPMC miss.           Port filter mode (PFM) per VLAN for L2 multicast, IPV4 multicast, and IPV6 multicast packets.           Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      | <ul> <li>Mirror-to-port receives unmodified packet for ingress mirroring.</li> </ul>                                                                                                                        |

| e Encapsulated remote switched port analyzer (ERSPAN) mirroring into a GRE tunnel.           Multiple packets can be generated in the StrataXGS architecture: one packet for the switched copy, and four mirror copies which can be of any type.           DSCP         Per port DSCP remarking.           DSCP to DSCP termarking.         DSCP to remove the second of any type.           Layer 3 Routing         Native support for IPV4 and IPV6 uncleast and multicast routing.           (IPV4, IPv6)         Native support for IPV4 and IPV6 uncleast and multicast routing.           Longest prefix match (LPM) based routing.         ECMPWCMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow label, and TCP/IUPP port.           Software-based aging support.         Routing of IPv6 packets.           True 128-bit IPv6 support as well as /64 support for LPM.           Virtual Routing and Forwarding (VRF)         VPN ID assigned based on ingress port, VLAN, or flow.           IP Multicast         Simultaneous L2 bridging and L3 routing.           Port filter mode (PFM) per VLAN for L2 multicast, IPv4 multicast, and IPv6 multicast packets.           Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.           IP multicast address consistency check with destination MAC address.           Pot filter mode (PFM) per VLAN for L2 multicast, IPv4 multicast, and IPv6 multicast packets.           Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | <ul> <li>Mirror-to-port receives modified packet for egress mirroring.</li> </ul>                                                                                                                           |

| <ul> <li>Multiple packets can be generated in the StrataXGS architecture: one packet for the switched copy, and four mirror copies which can be of any type.</li> <li>Payload zeroing and truncation for mirrored copies.</li> <li>DSCP</li> <li>Per port DSCP remarking.</li> <li>DSCP remarking based on a FP filter match.</li> <li>DSCP to IEEE 802.1 p mapping.</li> <li>Remap incoming DSCP to new outgoing DSCP.</li> <li>Layer 3 Routing</li> <li>Native support for IPv4 and IPv6 unicast and multicast routing.</li> <li>Direct-attached hosts in the L3 table.</li> <li>Longest prefix match (LPM) based routing.</li> <li>ECMPWCMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow label, and TCP/IDP port.</li> <li>Software-based aging support.</li> <li>Routing of IPv6 packets.</li> <li>True 128-bit IPv6 support as well as /64 support for LPM.</li> <li>Virtual Routing and</li> <li>Segmentation of L3 routing tables.</li> <li>VPN ID assigned based on ingress port, VLAN, or flow.</li> <li>Pheulticast</li> <li>Simultaneous L2 bridging and L3 routing.</li> <li>Flexible multicast packet replication.</li> <li>Optional source port checks.</li> <li>Dual lookup: (S, G, V) and (*, G, V).</li> <li>Ability to fall back to L2 multicast lookup on IPMC miss.</li> <li>Port filter mode (PFM) per VLAN for L2 multicast, IPV4 multicast, and IPV6 multicast packets.</li> <li>Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.</li> <li>IP multicast address consistency check with destination MAC address.</li> <li>Pied Tunneling</li> <li>IPV6-in-IPV6. The outer header is IPV6, and the payload is IPv6.</li> <li>IP-mil-Tv6 Tunnel: The outer header is IPV6, and the payload is IPv4.</li> <li>GRE Tunneling</li> <li>Supports IPV6 as sayload.</li> <li>Supports IPV6 as sayload.</li> <li>Supports IPV6 as sayload.</li> <li>Rules for assignment of VLAN based on fl</li></ul>                                                                                                                              |                      | <ul> <li>Remote switched port analyzer (RSPAN) mirroring, VLAN mirroring, flow mirroring</li> </ul>                                                                                                         |

| and four mirror copies which can be of any type.         Payload zeroing and truncation for mirrored copies.         DSCP       Per port DSCP remarking.         DSCP to IEEE 802.1p mapping.         Remap incoming DSCP to new outgoing DSCP.         Layer 3 Routing<br>(IPv4, IPv6)       Native support for IPv4 and IPv6 unicast and multicast routing.         Direct-attached hosts in the L3 table.       Longest prefix match (LPM) based routing.         ECMPWCMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow<br>label, and TCP/UDP port.         Software-based aging support.       Routing of IPv6 packets.         True 128-bit IPv6 support as well as /64 support for LPM.         Virtual Routing and<br>Forwarding (VRF)       VPN ID assigned based on ingress port, VLAN, or flow.         IP Multicast       Segmentation of L3 routing tables.         Pot filter mode (PFM) per VLAN for L2 multicast, IPv4 multicast, and IPv6 multicast packets.         Optional source port checks.       Dual lookup: (S, G, V) and (*, G, V).         Ability to fall back to L2 multicast lookup on IPMC miss.       Port filter mode (PFM) per VLAN for L2 multicast, IPv4 multicast, and IPv6 multicast packets.         Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.       IP multicast address consistency check with destination MAC address.         IP wo Fin-IPv6 Tunneling       IPv6-in-IPv6 Tunnel: The outer header is IPv6, and the payload is IPv6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      | <ul> <li>Encapsulated remote switched port analyzer (ERSPAN) mirroring into a GRE tunnel.</li> </ul>                                                                                                        |

| DSCP       Per port DSCP remarking.         DSCP remarking based on a FP filter match.         DSCP remarking based on a FP filter match.         DSCP to IEEE 802.19 mapping.         Remap incoming DSCP to new outgoing DSCP.         Layer 3 Routing<br>(IPv4, IPv6)         Pietc-attached hosts in the L3 table.         Longest prefix match (LPM) based routing.         ECMP/WCMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow<br>label, and TCP/UDP port.         Software-based aging support.         Routing of IPv6 packets.         Tore 128-bit IPv6 support as well as /64 support for LPM.         Virtual Routing and         Forwarding (VRF)         VPN ID assigned based on ingress port, VLAN, or flow.         IP Multicast         Simultaneous L2 brid IPv6 support as well as /64 support for LPM.         Simultaneous L2 bridging and L3 routing.         Flexible multicast packet replication.         Optional source port checks.         Dual lookup: {5, G, V) and {*, G, V}.         Ability to fall back to L2 multicast lookup on IPMC miss.         Port filter mode (PFM) per VLAN for L2 multicast, IPv4 multicast, and IPv6 multicast packets.         Control trapping of Unknown IPMC packets to CPU on a per VLAN, per IP-type basis.         IP multicast address consistency check with destination MAC address.         I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |                                                                                                                                                                                                             |

| BCCP remarking based on a FP filter match.         DSCP to IEEE 802.1p mapping.         Remap incoming DSCP to new outgoing DSCP.         Layer 3 Routing<br>(IPv4, IPv6)         Native support for IPv4 and IPv6 unicast and multicast routing.         Longest prefix match (LPM) based routing.         ECMPWCMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow<br>label, and TCP/UDP port.         Software-based aging support.         Routing of IPv6 packets.         True 128-bit IPv6 support as well as /64 support for LPM.         Virtual Routing and<br>Forwarding (VRF)         PVN ID assigned based on ingress port, VLAN, or flow.         IP Multicast         Simultaneous L2 bridging and L3 routing.         Flexible multicast packet replication.         Optional source port checks.         Dual lookup: (S, G, V) and (*, G, V).         Ability to fall back to L2 multicast lookup on IPMC miss.         Port filter mode (PFM) per VLAN for L2 multicast, IPv4 multicast, and IPv6 multicast packets.         Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.         IPv6 Tunneling       IPv6-in-IPv6 Tunnet: The outer header is IPv6, and the payload is IPv4.         GRE Tunneling       Supports IPv4 as payload.         Preclassification<br>ContentAware <sup>TM</sup> processor<br>(VCAP)       Support for single-wide and double-wide modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      | <ul> <li>Payload zeroing and truncation for mirrored copies.</li> </ul>                                                                                                                                     |

| BSCP to IEEE 02.1p mapping.         Remap incoming DSCP to new outgoing DSCP.         Layer 3 Routing         (IPv4, IPv6)         Expert 3 Routing         (IPv4, IPv6)         ECMP/WCMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow<br>label, and TCP/UDP port.         Software-based aging support.         Routing of IPv6 support as well as /64 support for LPM.         Virtual Routing and<br>Forwarding (VRF)         VPN ID assigned based on ingress port, VLAN, or flow.         IP Multicast         Simultaneous L2 bridging and L3 routing.         Filexible multicast packet replication.         Optional source port checks.         Dual lookup: (S, G, V) and (*, G, V).         Ability to fall back to L2 multicast lookup on IPMC miss.         Port filter mode (PFM) per VLAN for L2 multicast, and IPv6 multicast packets.         Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.         IP Multicast         Supports IPv4 as payload.         Preclassification<br>Content/Aware™ processor<br>(VCAP)         Supports IPv4 as sayload.         Preclassification<br>Content/Aware™ processor<br>(VCAP)         Protection Switching   Declated hardware support for the following:<br><ul> <li>MPLS fast reroute (FRR).</li> <li>MPLS fast reroute (FRR).</li> <li>MPLS fast reroute (FRR).</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DSCP                 | Per port DSCP remarking.                                                                                                                                                                                    |

| Image: Remap incoming DSCP to new outgoing DSCP.         Layer 3 Routing (IPV4, IPV6)         Pitted: Attached hosts in the L3 table.         Longest prefix match (LPM) based routing.         ECMPWCMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow label, and TCP/UDP port.         Software-based aging support.         Routing of IPv6 packets.         True 128-bit IPv6 support as well as /64 support for LPM.         Virtual Routing and Forwarding (VRF)         Power Dissigned based on ingress port, VLAN, or flow.         IP Multicast       Simultaneous L2 bridging and L3 routing.         Flexible multicast packet replication.         Optional source port checks.         Dual lookup: (S, G, V) and (*, G, V).         Ability to fall back to L2 multicast lookup on IPMC miss.         Port filter mode (PFM) per VLAN for L2 multicast, IPV4 multicast, and IPV6 multicast packets.         Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.         IP multicast address consistency check with destination MAC address.         IPv6 in-IPV6 Tunnel: The outer header is IPV6, and the payload is IPv4.         GRE Tunneling       Supports IPV4 as payload.         Preclassification ContentAware 1M processor (VCAP)       Support for single-wide and double-wide modes.         Field selectors on per port, per slice, and per packet type basis.       Field selectors o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |                                                                                                                                                                                                             |

| Layer 3 Routing<br>(IPv4, IPv6)       Native support for IPv4 and IPv6 unicast and multicast routing.         UPv4, IPv6)       Direct-attached hosts in the L3 table.         Longest prefix match (LPM) based routing.       ECMPWCMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow<br>label, and TCP/UDP port.         Software-based aging support.       Routing of IPv6 packets.         True 128-bit IPv6 Support as well as /64 support for LPM.         Virtual Routing and<br>Forwarding (VRF)       Segmentation of L3 routing tables.         VFN ID assigned based on ingress port, VLAN, or flow.         IP Multicast       Simultaneous L2 bridging and L3 routing.         Flexible multicast packet replication.       Optional source port checks.         Dual lookup: (S, G, V) and (*, G, V).       Ability to fall back to L2 multicast lookup on IPMC miss.         Port filter mode (PFM) per VLAN for L2 multicast, Pv4 multicast, and IPv6 multicast packets.         Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.         IP wdfucast IPv6 Tunneling       IPv6 in-IPv6: The outer header is IPv6, and the payload is IPv6.         IP-in-IPv6 Tunnel: The outer header is IPv6, and the payload is IPv4.         Supports IPv6 as payload.         Supp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |                                                                                                                                                                                                             |

| <ul> <li>(IPv4, IPv6)</li> <li>Direct-attached hosts in the L3 table.</li> <li>Longest prefix match (LPM) based routing.</li> <li>ECMP/WCMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow label, and TCP/UDP port.</li> <li>Software-based aging support.</li> <li>Routing of IPv6 packets.</li> <li>True 128-bit IPv6 support as well as /64 support for LPM.</li> <li>Virtual Routing and</li> <li>Segmentation of L3 routing tables.</li> <li>VPN ID assigned based on ingress port, VLAN, or flow.</li> <li>IP Multicast</li> <li>Simultaneous L2 bridging and L3 routing.</li> <li>Flexible multicast packet replication.</li> <li>Optional source port checks.</li> <li>Dual lookup: {S, G, V} and {*, G, V}.</li> <li>Ability to fall back to L2 multicast lookup on IPMC miss.</li> <li>Port filter mode (PFM) per VLAN for L2 multicast, and IPv6 multicast packets.</li> <li>Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.</li> <li>IP multicast address consistency check with destination MAC address.</li> <li>IP multicast address consistency check with destination MAC address.</li> <li>IP multicast address consistency check with destination MAC address.</li> <li>IP-in-IPv6 Tunneling</li> <li>IP-in-IPv6 Tune outer header is IPv6, and the payload is IPv4.</li> <li>Supports IPv4 as payload.</li> <li>Supports IPv4 as payload.</li> <li>Supports IPv4 as payload.</li> <li>Supports IPv6 as payload.</li> <li>Supports IPv6 as payload.</li> <li>Support single-wide and double-wide modes.</li> <li>Field selectors on per port, per slice, and per packet type basis.</li> <li>Ability to add or replace VLAN tag, change priority, assign classification ID, drop.</li> <li>Protection Switching</li> <li>Dedicated hardware support for the following:</li> <li>MPLS fast reroute (FRR).</li> </ul>                                                                                                                                                                                                            |                      |                                                                                                                                                                                                             |

| <ul> <li>(IPv4, IPv6)</li> <li>Direct-attached hosts in the L3 table.</li> <li>Longest prefix match (LPM) based routing.</li> <li>ECMP/WCMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow label, and TCP/UDP port.</li> <li>Software-based aging support.</li> <li>Routing of IPv6 packets.</li> <li>True 128-bit IPv6 support as well as /64 support for LPM.</li> <li>Virtual Routing and</li> <li>Segmentation of L3 routing tables.</li> <li>VPN ID assigned based on ingress port, VLAN, or flow.</li> <li>IP Multicast</li> <li>Simultaneous L2 bridging and L3 routing.</li> <li>Flexible multicast packet replication.</li> <li>Optional source port checks.</li> <li>Dual lookup: {S, G, V} and {*, G, V}.</li> <li>Ability to fall back to L2 multicast lookup on IPMC miss.</li> <li>Port filter mode (PFM) per VLAN for L2 multicast, and IPv6 multicast packets.</li> <li>Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.</li> <li>IP multicast address consistency check with destination MAC address.</li> <li>IP multicast address consistency check with destination MAC address.</li> <li>IP multicast address consistency check with destination MAC address.</li> <li>IP-in-IPv6 Tunneling</li> <li>IP-in-IPv6 Tune outer header is IPv6, and the payload is IPv4.</li> <li>Supports IPv4 as payload.</li> <li>Supports IPv4 as payload.</li> <li>Supports IPv4 as payload.</li> <li>Supports IPv6 as payload.</li> <li>Supports IPv6 as payload.</li> <li>Support single-wide and double-wide modes.</li> <li>Field selectors on per port, per slice, and per packet type basis.</li> <li>Ability to add or replace VLAN tag, change priority, assign classification ID, drop.</li> <li>Protection Switching</li> <li>Dedicated hardware support for the following:</li> <li>MPLS fast reroute (FRR).</li> </ul>                                                                                                                                                                                                            | Laver 3 Routing      | Native support for IPv4 and IPv6 unicast and multicast routing.                                                                                                                                             |

| Image: Project Structure       Image: Project Structure         Image: Project Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (IPv4, IPv6)         |                                                                                                                                                                                                             |

| • ECMPWCMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow label, and TCP/UDP port.         • Software-based aging support.         • Routing of IPv6 packets.         • True 128-bit IPv6 support as well as /64 support for LPM.         Virtual Routing and Forwarding (VRF)         • Segmentation of L3 routing tables.         • VPN ID assigned based on ingress port, VLAN, or flow.         IP Multicast       • Simultaneous L2 bridging and L3 routing.         • Flexible multicast packet replication.       • Optional source port checks.         • Dual lookup: (S, G, V) and (*, G, V).       • Ability to fall back to L2 multicast lookup on IPMC miss.         • Port filter mode (PFM) per VLAN for L2 multicast, IPV4 multicast, and IPV6 multicast packets.         • Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.         IPV6 Tunneling       • IPv6-in-IPv6: The outer header is IPv6, and the payload is IPv6.         IP-in-IPv6 Tunnel: The outer header is IPv6, and the payload is IPv4.       Supports IPv4 as payload.         GRE Tunneling       • Supports IPv4 as payload.       Supports IPv4 as payload.         • Supports IPv6 as assignment of VLAN based on flexible criteria, block packets, bind MAC address with IP address, and assign VRF ID.       • Support for single-wide and double-wide modes.         • Field selectors on per port, per slice, and per packet type basis.       • Ability to add or replace VLAN tag, change priority, assig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |                                                                                                                                                                                                             |

| Routing of IPv6 packets.         True 128-bit IPv6 support as well as /64 support for LPM.         Virtual Routing and<br>Forwarding (VRF)         Segmentation of L3 routing tables.         VPN ID assigned based on ingress port, VLAN, or flow.         IP Multicast         Simultaneous L2 bridging and L3 routing.         Flexible multicast packet replication.         Optional source port checks.         Dual lookup: {S, G, V} and {*, G, V}.         Ability to fall back to L2 multicast lookup on IPMC miss.         Port filter mode (PFM) per VLAN for L2 multicast, IPv4 multicast, and IPv6 multicast packets.         Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.         IP wolticast address consistency check with destination MAC address.         IPv6 Tunneling       IPv6-in-IPv6: The outer header is IPv6, and the payload is IPv6.         IP-in-IPv6 Tunnel: The outer header is IPv6, and the payload is IPv4.         GRE Tunneling       Supports IPv4 as payload.         Preclassification<br>ContentAware <sup>TM</sup> processor<br>(VCAP)       Supports IPv6 assignment of VLAN based on flexible criteria, block packets, bind MAC address with IP<br>address, and assign VRF ID.         Support for single-wide and double-wide modes.       Field selectors on per port, per slice, and per packet type basis.         Ability to add or replace VLAN tag, change priority, assign classification ID, drop.       Poteicated hardware support for the following:<br>MPLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      | ECMP/WCMP routing: ECMP path resolution based on source/source IP address, Protocol, IPv6 flow                                                                                                              |

| • True 128-bit IPv6 support as well as /64 support for LPM.         Virtual Routing and       • Segmentation of L3 routing tables.         Forwarding (VRF)       • VPN ID assigned based on ingress port, VLAN, or flow.         IP Multicast       • Simultaneous L2 bridging and L3 routing.         • Flexible multicast packet replication.       • Optional source port checks.         • Dual lookup: {S, G, V} and {*, G, V}.       • Ability to fall back to L2 multicast lookup on IPMC miss.         • Port filter mode (PFM) per VLAN for L2 multicast, IPv4 multicast, and IPv6 multicast packets.         • Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.         IP multicast address consistency check with destination MAC address.         IPv6 Tunneling       • IPv6-in-IPv6: The outer header is IPv6, and the payload is IPv6.         • IP-in-IPv6 Tunnel: The outer header is IPv6, and the payload is IPv4.         GRE Tunneling       • Supports IPv4 as payload.         • Supports IPv6 as payload.       • Supports IPv6 as payload.         • Support for single-wide and double-wide modes.       • Field selectors on per port, per slice, and per packet type basis.         • Field selectors on per port, per slice, and per packet type basis.       • Ability to add or replace VLAN tag, change priority, assign classification ID, drop.         Protection Switching       Dedicated hardware support for the following:       MPLS fast reroute (FRR).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      | <ul> <li>Software-based aging support.</li> </ul>                                                                                                                                                           |

| Virtual Routing and<br>Forwarding (VRF) <ul> <li>Segmentation of L3 routing tables.</li> <li>VPN ID assigned based on ingress port, VLAN, or flow.</li> </ul> IP Multicast <ul>                       Simultaneous L2 bridging and L3 routing.                       Flexible multicast packet replication.                       Optional source port checks.                       Dual lookup: {S, G, V} and {*, G, V}.                       Ability to fall back to L2 multicast lookup on IPMC miss.                        Port filter mode (PFM) per VLAN for L2 multicast, IPV4 multicast, and IPv6 multicast packets.                          Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.                           IP multicast address consistency check with destination MAC address.                               IPv6-in-IPv6: The outer header is IPv6, and the payload is IPv6.                           IP-in-IPv6 Tunnel: The outer header is IPv6, and the payload is IPv4.                             Supports IPv4 as payload.                         Supports IPv6 as payload.                         Supports IPv6 as payload.                         Supports IPv6 as payload.                           Supports IPv6 as payload.                          Supports IPv6 as payload.                         Supports IPv6 as payload.                         Supports IPv6 as payload.                         Support for single-wide and double-wide modes.                         Field selectors on per port, per slice, and per packet type basis.                         Ability to add or replace VLAN tag, change priority, assign classification ID, drop.                         Protection Switching            Pretecti</ul>                                                                                                                                                                                                                                                                                                      |                      | <ul> <li>Routing of IPv6 packets.</li> </ul>                                                                                                                                                                |

| Forwarding (VRF)       • VPN ID assigned based on ingress port, VLAN, or flow.         IP Multicast       • Simultaneous L2 bridging and L3 routing.         • Flexible multicast packet replication.       • Optional source port checks.         • Dual lookup: {\$, G, V} and {*, G, V}.       • Ability to fall back to L2 multicast lookup on IPMC miss.         • Port filter mode (PFM) per VLAN for L2 multicast, IPv4 multicast, and IPv6 multicast packets.         • Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.         IP multicast address consistency check with destination MAC address.         IPv6 Tunneling       • IPv6-in-IPv6: The outer header is IPv6, and the payload is IPv6.         • IP-in-IPv6 Tunnel: The outer header is IPv6, and the payload is IPv4.         GRE Tunneling       • Supports IPv4 as payload.         • Supports IPv6 as payload.       • Supports IPv6 as payload.         • Supports IPv6 as payload.       • Supports IPv6 as payload.         • Supports IPv6 as payload.       • Supports IPv6 as payload.         • Support for single-wide and double-wide modes.       • Field selectors on per port, per slice, and per packet type basis.         • Field selectors on per port, per slice, and per packet type basis.       • Ability to add or replace VLAN tag, change priority, assign classification ID, drop.         Protection Switching       Dedicated hardware support for the following:       MPLS fast reroute (FRR). <td></td> <td><ul> <li>True 128-bit IPv6 support as well as /64 support for LPM.</li> </ul></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      | <ul> <li>True 128-bit IPv6 support as well as /64 support for LPM.</li> </ul>                                                                                                                               |

| Forwarding (VRF)       • VPN ID assigned based on ingress port, VLAN, or flow.         IP Multicast       • Simultaneous L2 bridging and L3 routing.         • Flexible multicast packet replication.       • Optional source port checks.         • Dual lookup: {\$, G, V} and {*, G, V}.       • Ability to fall back to L2 multicast lookup on IPMC miss.         • Port filter mode (PFM) per VLAN for L2 multicast, IPv4 multicast, and IPv6 multicast packets.         • Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.         IP multicast address consistency check with destination MAC address.         IPv6 Tunneling       • IPv6-in-IPv6: The outer header is IPv6, and the payload is IPv6.         • IP-in-IPv6 Tunnel: The outer header is IPv6, and the payload is IPv4.         GRE Tunneling       • Supports IPv4 as payload.         • Supports IPv6 as payload.       • Supports IPv6 as payload.         • Supports IPv6 as payload.       • Supports IPv6 as payload.         • Supports IPv6 as payload.       • Supports IPv6 as payload.         • Support for single-wide and double-wide modes.       • Field selectors on per port, per slice, and per packet type basis.         • Field selectors on per port, per slice, and per packet type basis.       • Ability to add or replace VLAN tag, change priority, assign classification ID, drop.         Protection Switching       Dedicated hardware support for the following:       MPLS fast reroute (FRR). <td>Virtual Routing and</td> <td>Segmentation of L3 routing tables.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Virtual Routing and  | Segmentation of L3 routing tables.                                                                                                                                                                          |

| <ul> <li>Flexible multicast packet replication.</li> <li>Optional source port checks.</li> <li>Dual lookup: {S, G, V} and {*, G, V}.</li> <li>Ability to fall back to L2 multicast lookup on IPMC miss.</li> <li>Port filter mode (PFM) per VLAN for L2 multicast, IPv4 multicast, and IPv6 multicast packets.</li> <li>Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.</li> <li>IP multicast address consistency check with destination MAC address.</li> <li>IPv6-in-IPv6: The outer header is IPv6, and the payload is IPv6.</li> <li>IP-in-IPv6 Tunnel: The outer header is IPv6, and the payload is IPv4.</li> <li>GRE Tunneling</li> <li>Supports IPv4 as payload.</li> <li>Supports IPv6 as payload.</li> <li>Supports IPv6 as payload.</li> <li>Supports IPv6 as payload.</li> <li>Support for assignment of VLAN based on flexible criteria, block packets, bind MAC address with IP address, and assign VRF ID.</li> <li>Support for single-wide and double-wide modes.</li> <li>Field selectors on per port, per slice, and per packet type basis.</li> <li>Ability to add or replace VLAN tag, change priority, assign classification ID, drop.</li> <li>Protection Switching</li> <li>Dedicated hardware support for the following:</li> <li>MPLS fast reroute (FRR).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Forwarding (VRF)     |                                                                                                                                                                                                             |

| <ul> <li>Optional source port checks.</li> <li>Dual lookup: {S, G, V} and {*, G, V}.</li> <li>Ability to fall back to L2 multicast lookup on IPMC miss.</li> <li>Port filter mode (PFM) per VLAN for L2 multicast, IPV4 multicast, and IPv6 multicast packets.</li> <li>Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.</li> <li>IP multicast address consistency check with destination MAC address.</li> <li>IPv6-in-IPv6: The outer header is IPv6, and the payload is IPv6.</li> <li>IP-in-IPv6 Tunnel: The outer header is IPv6, and the payload is IPv4.</li> <li>GRE Tunneling</li> <li>Supports IPv4 as payload.</li> <li>Supports IPv6 as payload.</li> <li>Support for single-wide and double-wide modes.</li> <li>Field selectors on per port, per slice, and per packet type basis.</li> <li>Ability to add or replace VLAN tag, change priority, assign classification ID, drop.</li> <li>Protection Switching</li> <li>Dedicated hardware support for the following:</li> <li>MPLS fast reroute (FRR).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IP Multicast         | <ul> <li>Simultaneous L2 bridging and L3 routing.</li> </ul>                                                                                                                                                |

| <ul> <li>Dual lookup: {S, G, V} and {*, G, V}.</li> <li>Ability to fall back to L2 multicast lookup on IPMC miss.</li> <li>Port filter mode (PFM) per VLAN for L2 multicast, IPv4 multicast, and IPv6 multicast packets.</li> <li>Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.</li> <li>IP multicast address consistency check with destination MAC address.</li> <li>IPv6 Tunneling</li> <li>IPv6-in-IPv6: The outer header is IPv6, and the payload is IPv6.</li> <li>IP-in-IPv6 Tunnel: The outer header is IPv6, and the payload is IPv4.</li> <li>GRE Tunneling</li> <li>Supports IPv4 as payload.</li> <li>Supports IPv6 as payload.</li> <li>Support for single-wide and double-wide modes.</li> <li>Field selectors on per port, per slice, and per packet type basis.</li> <li>Ability to add or replace VLAN tag, change priority, assign classification ID, drop.</li> <li>Protection Switching</li> <li>Dedicated hardware support for the following:</li> <li>MPLS fast reroute (FRR).</li> </ul>                                                                                                                                                                                                                                                                                                                                                   |                      |                                                                                                                                                                                                             |

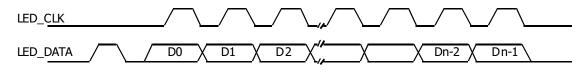

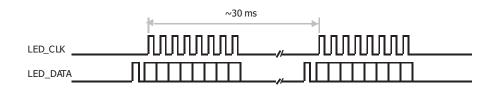

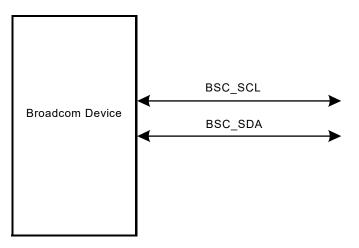

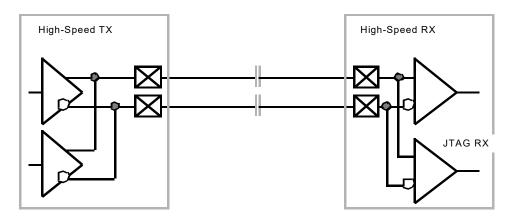

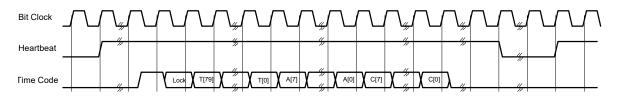

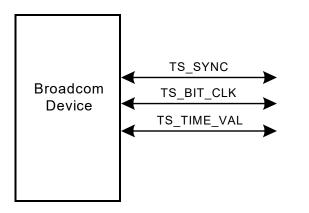

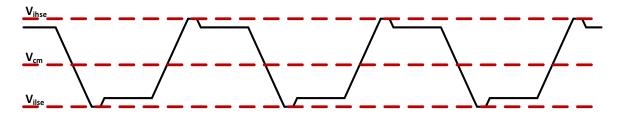

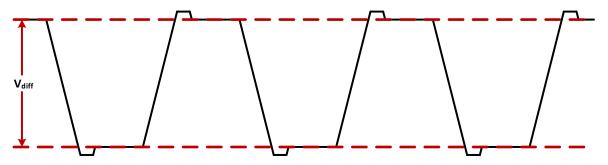

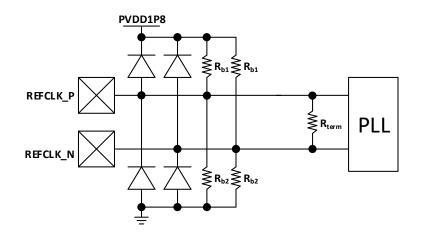

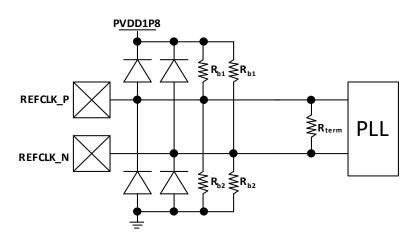

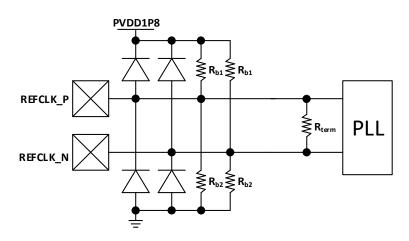

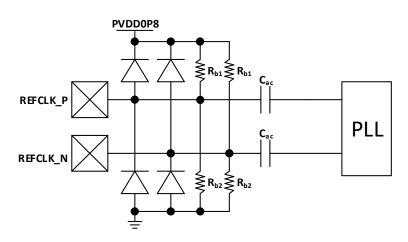

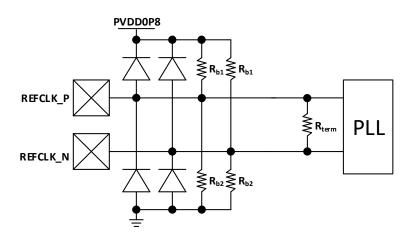

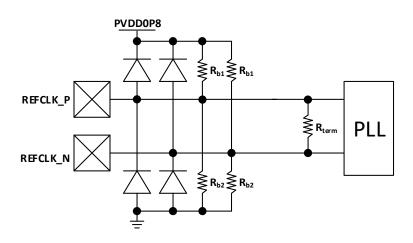

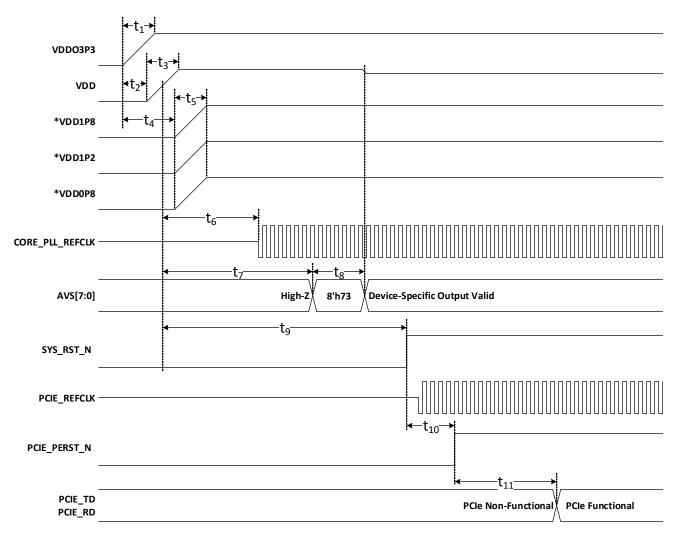

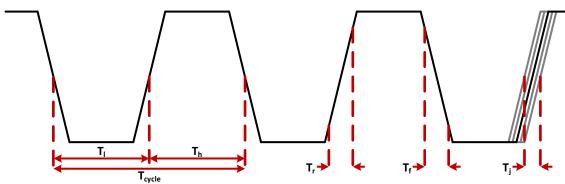

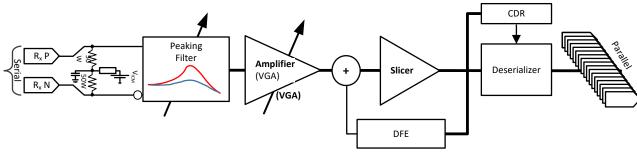

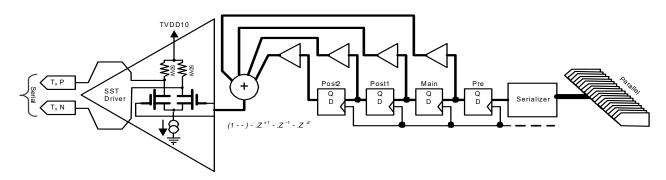

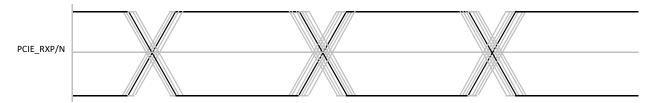

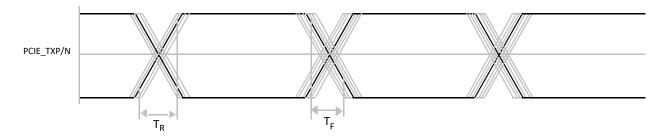

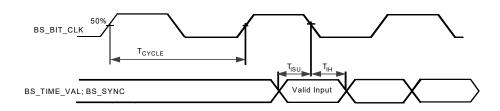

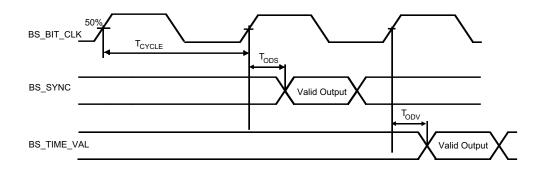

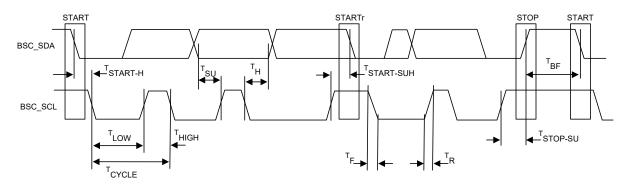

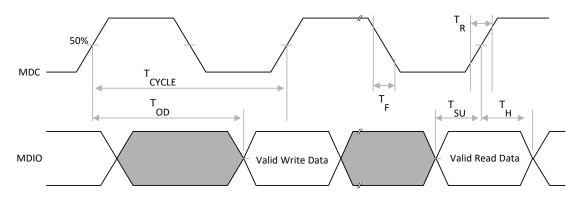

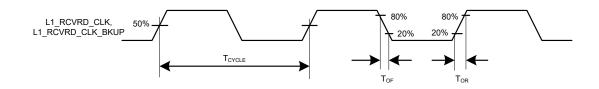

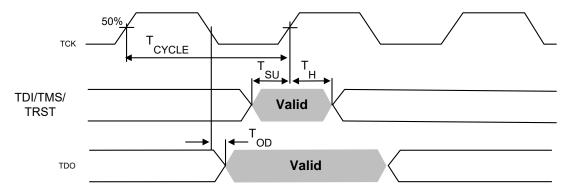

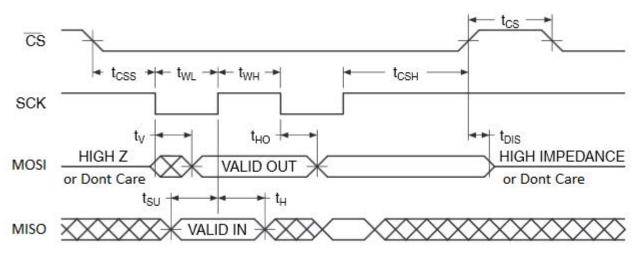

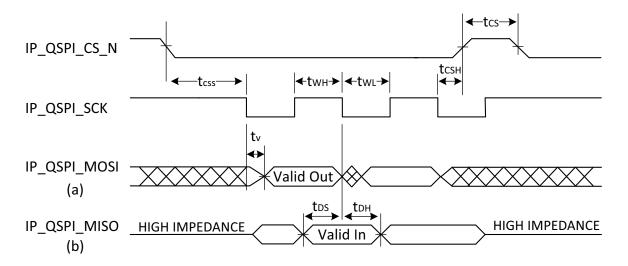

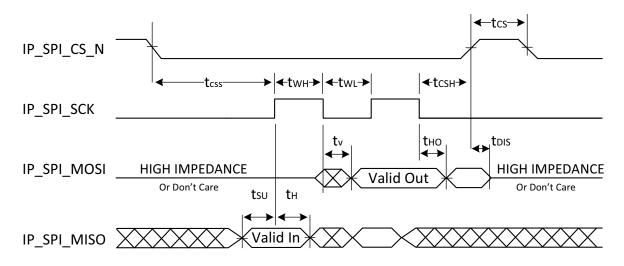

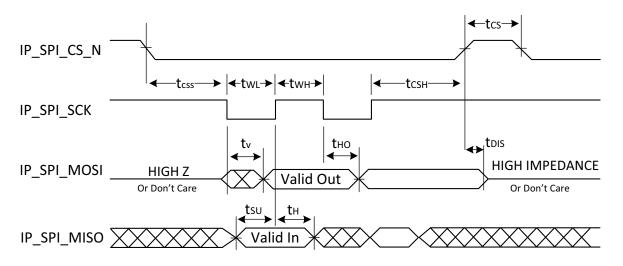

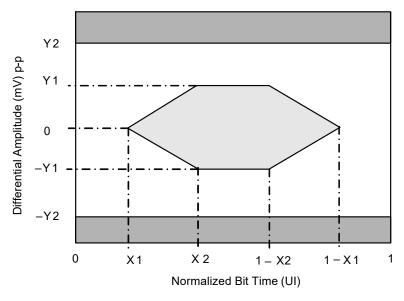

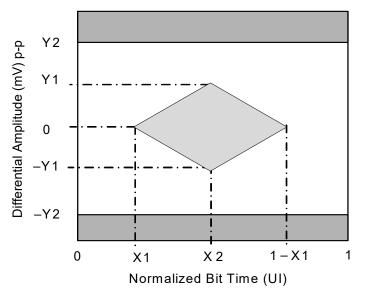

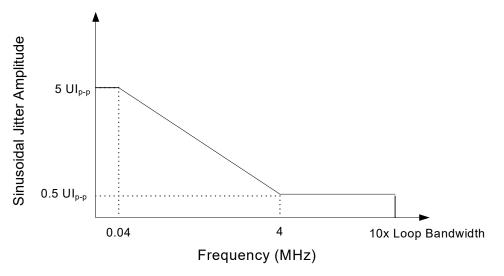

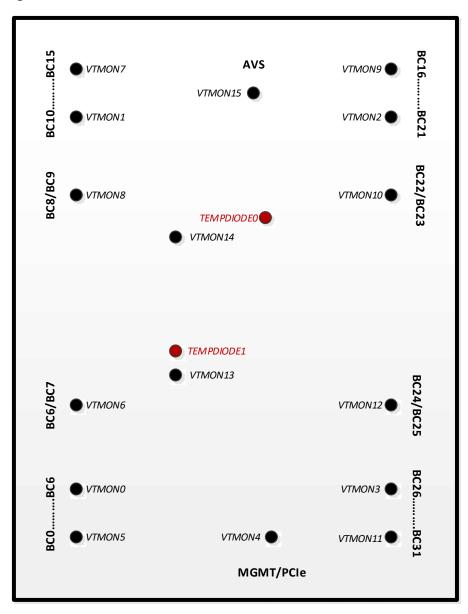

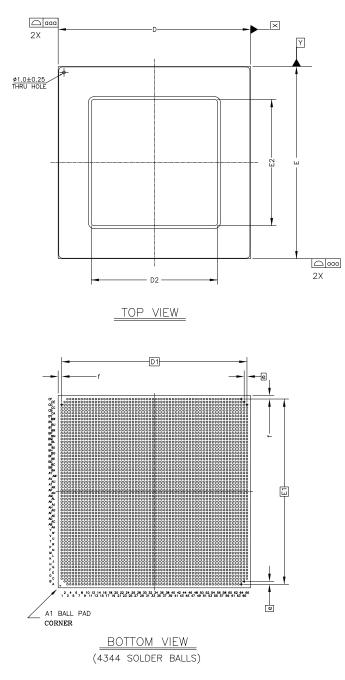

| <ul> <li>Dual lookup: {S, G, V} and {*, G, V}.</li> <li>Ability to fall back to L2 multicast lookup on IPMC miss.</li> <li>Port filter mode (PFM) per VLAN for L2 multicast, IPv4 multicast, and IPv6 multicast packets.</li> <li>Control trapping of unknown IPMC packets to CPU on a per VLAN, per IP-type basis.</li> <li>IP multicast address consistency check with destination MAC address.</li> <li>IPv6 Tunneling</li> <li>IPv6-in-IPv6: The outer header is IPv6, and the payload is IPv6.</li> <li>IP-in-IPv6 Tunnel: The outer header is IPv6, and the payload is IPv4.</li> <li>GRE Tunneling</li> <li>Supports IPv4 as payload.</li> <li>Supports IPv6 as payload.</li> <li>Support for single-wide and double-wide modes.</li> <li>Field selectors on per port, per slice, and per packet type basis.</li> <li>Ability to add or replace VLAN tag, change priority, assign classification ID, drop.</li> <li>Protection Switching</li> <li>Dedicated hardware support for the following:</li> <li>MPLS fast reroute (FRR).</li> </ul>                                                                                                                                                                                                                                                                                                                                                   |                      |                                                                                                                                                                                                             |